## System-Management IC with Programmable Quad **Voltage Monitoring and Supervisory Functions**

### **Preliminary Technical Data**

### **FEATURES**

- Two Device-Enabling Outputs with Six Programmable Monitoring Inputs (Table 1)

- Two 30V Monitoring Inputs with Shutdown Control of **External Devices:**

- Programmable Over-voltage, Under-voltage, Turn-on, Turn-off Thresholds, and Shutdown timinas

- Shutdown Warning with Fault Detection

- Two 5V Monitoring Inputs with Reset Control of External Devices:

- Programmable Reset Thresholds and Hold Time • Two Supervisory Functions:

- Watchdog Reset Controller with Programmable **Timeout and Selectable Floating Input**

- Manual Reset Control for External Devices

- Digital Interface and Programmability:

- o I<sup>2</sup>C<sup>®</sup> Compatible Interface

- **OTP<sup>1</sup> for Permanent Threshold and Timing Settings** 0

- **OTP Overwritten Capable for Dynamic Adjustments** 0

- Power Up by Edge Triggered Signal

- Power Down by I<sup>2</sup>C Software

- Operating Range:

- Supply Voltage 6.0V to 30V

- Temp Range -40°C to +125°C 0

- Low Shutdown Current: 10µA 0

- High-Voltage-Input Anti-migration Shielding Pinouts

#### **APPLICATIONS**

- **Automotive Systems**

- **Network Equipment**

- **Computers, Controllers, and Embedded Systems**

#### **GENERAL DESCRIPTION**

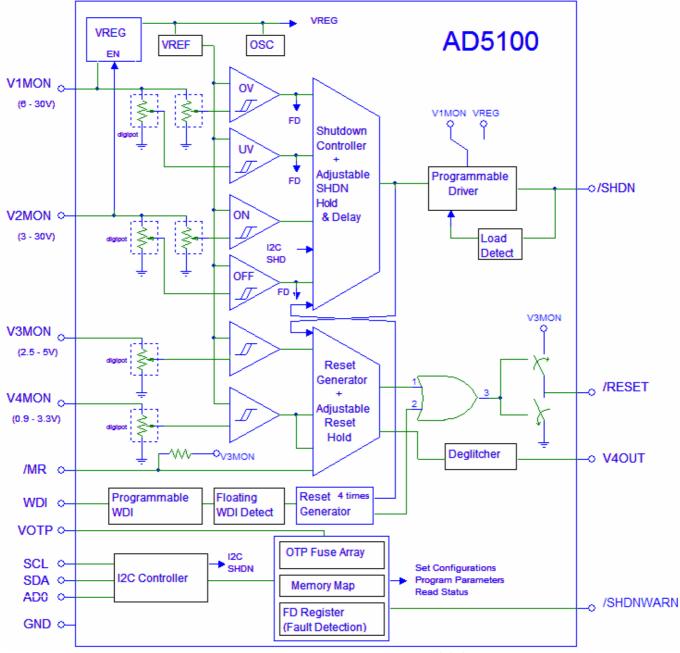

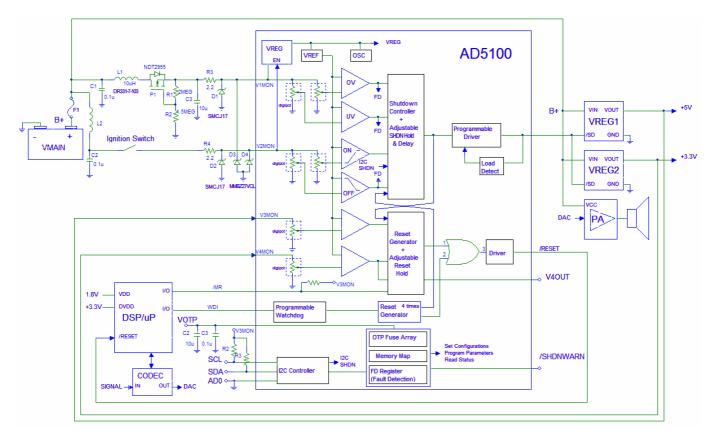

The AD5100 is a programmable system-management IC that combines 4-channel of voltage monitoring and a watchdog supervision that can be used to shutdown external supplies, reset processors, or disable any other system electronics when the systems malfunction. The AD5100 can also be used to protect system under faulty condition of improper devices power up sequencing. The AD5100 can monitor two 30V inputs with shutdown and reset controls, one 2.5V-5.0V and one 0.9V-3.3V monitoring inputs with reset control, a robust watchdog reset controller. Most monitoring input thresholds and timing settings can be programmed on the fly or permanently set in the factory with the OTP feature.

AD5100

The AD5100 is versatile for system-monitoring applications where critical  $\mu$ P, DSP, and embedded systems operate under harsh conditions such as automotive, industrial, or communications network environments

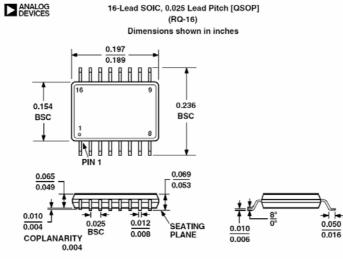

The AD5100 is available in compact QSOP-16 and can operate in an extended automotive temperature range from -40°C to +125°C.

<sup>1</sup>.One Time Programmable EPROM – Unlimited Adjustment Before OTP Execution. <sup>2</sup> With Programmable Threshold and Programmable Delay.

| Input             | Monitoring<br>Range <sup>2</sup> | Shutdown<br>Control | Reset<br>Cont<br>rol | Fault<br>Dete<br>ctio<br>n |

|-------------------|----------------------------------|---------------------|----------------------|----------------------------|

| V <sub>1MON</sub> | 6 – 30 V                         | $\checkmark$        |                      | $\checkmark$               |

| V <sub>2MON</sub> | 3 – 30 V                         | $\checkmark$        |                      | $\checkmark$               |

| V <sub>3MON</sub> | 2.5 – 5.0 V                      |                     |                      | $\checkmark$               |

| $V_{4MON}$        | 0.9 – 3.3 V                      |                     | $\checkmark$         | $\checkmark$               |

| WDI               | 0 – 5 V                          | $\checkmark$        | $\checkmark$         |                            |

| MR                | 0 – 5 V                          |                     | $\checkmark$         |                            |

Table 1. AD5100 General Inputs and Output Information

Rev. PrJ

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

FUNCTIONAL BLOCK DIAGRAM

Figure 1. Functional Block Diagram

# **Electrical Characteristics**

$6V \leq V_{1MON} \leq 30V$  and  $3V \leq V_{2MON} \leq 30V$ , -40°C  $\leq T_A \leq$  +125°C, unless otherwise noted.

| Table | 2. |  |  |

|-------|----|--|--|

| Parameter                                          | Symbol                                | Conditions                                                      | Min                    | Typ <sup>1</sup> | Max  | Unit |

|----------------------------------------------------|---------------------------------------|-----------------------------------------------------------------|------------------------|------------------|------|------|

| HIGH-VOLTAGE MONITORING INPUTS                     | V1MON, V2MON AND SI                   | HDN, SHDNWARN OUTPUT                                            |                        |                  |      |      |

| Input Resistance                                   | RIN_V1MON, RIN_V2MON                  |                                                                 |                        | 60               |      | KΩ   |

| V <sub>1MON</sub>                                  |                                       |                                                                 |                        |                  |      |      |

| OV, UV Threshold Tolerance                         | ΔΟΥ, ΔUV                              | $T_A = 25^{\circ}C$                                             | -1.5                   |                  | +1.5 | %    |

| (Figure 5 and Table 5a)                            |                                       | $T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C$                  | -2                     |                  | +2   | %    |

|                                                    |                                       | $T_A = -40^{\circ}C \text{ to } 125^{\circ}C$                   | -3                     |                  | +3   | %    |

| Hysteresis                                         |                                       |                                                                 |                        | 1.5              |      | %    |

| Programmable Shutdown Hold<br>Time Tolerance       | $\Delta t_{1SD\_HOLD}$                | Does not apply to code 0x7                                      | -10                    |                  | +10  | %    |

| (Figure 5 and Table 6a)                            |                                       |                                                                 |                        |                  |      |      |

| Programmable Shutdown Delay<br>Tolerance           | $\Delta t_{1SD\_DELAY}$               | Does not apply to code 0x7                                      | -10                    |                  | +10  | %    |

| (Figure 4 and Table 6a)                            |                                       |                                                                 |                        |                  |      |      |

| Fault Detection Delay                              | t <sub>FD_DELAY</sub>                 |                                                                 |                        | 70               |      | μs   |

| Glitch-Immune Time                                 | <b>t</b> GLITCH                       |                                                                 |                        | 50               |      | μs   |

| V <sub>2MON</sub>                                  |                                       |                                                                 |                        |                  |      |      |

| On, Off Threshold Tolerance <sup>2</sup>           | $\Delta On$ , $\Delta Off$            | $T_A = 25^{\circ}C$                                             | -1.5                   |                  | +1.5 | %    |

| (Figure 5 and Table 5a)                            |                                       | $T_{A} = -40^{\circ}C \text{ to } 85^{\circ}C$                  | -2                     |                  | +2   | %    |

|                                                    |                                       | $T_A = -40^{\circ}C$ to 125°C                                   | -3                     |                  | +3   | %    |

| Hysteresis                                         |                                       |                                                                 |                        | 1.5              |      | %    |

| Turn-On Programmable SHDN Hold<br>Time Tolerance   | $\Delta t_{2SD_{HOLD}}$               | Does not apply to code 0x7                                      | -10                    |                  | +10  | %    |

| (Figure 5 and Table 6a)                            |                                       |                                                                 |                        |                  |      |      |

| Turn-Off Programmable SHDN<br>Delay Time Tolerance | $\Delta t_{2SD\_DELAY}$               | Does not apply to code 0x7                                      | -10                    |                  | +10  | %    |

| (Figure 5 and Table 6a)                            |                                       |                                                                 |                        |                  |      |      |

| Fault Detection Delay                              | <b>t</b> fd_delay                     | V <sub>2MON_OFF</sub> only                                      |                        | 70               |      | μs   |

| Glitch Immune Time                                 | t <sub>GUTCH</sub>                    |                                                                 |                        | 50               |      | μs   |

| SHDN Output High                                   | V <sub>он</sub>                       | V <sub>RAIL</sub> =V <sub>REG</sub> , I <sub>SOURCE</sub> =40uA | 2.4                    |                  |      | V    |

| SHDN Output High                                   | V <sub>он</sub>                       | VRAIL=V1MON, ISOURCE=600uA                                      | V <sub>1MON</sub> -0.5 |                  |      | v    |

| SHDN Output Low                                    | Vol                                   | I <sub>SINK</sub> =1.6mA                                        |                        |                  | 0.4  | v    |

| SHDN Output Low                                    | Vol                                   | V <sub>1MON</sub> =12V, I <sub>SINK</sub> =40mA                 |                        | 1.7              | 3    | v    |

| SHDN Sink Current                                  | Isink                                 | V <sub>1MON</sub> =12V, SHDN forced to 12V                      |                        | 10               | 15   | mA   |

| SHDNWARN (Open Drain Output)                       |                                       |                                                                 |                        |                  |      |      |

| SHDNWARN Inactive Leakage                          | Ioh_shdnwarn                          |                                                                 |                        | 1                |      | μΑ   |

| SHDNWARN Active                                    | Vol_shdnwarn                          | Isink = 3mA                                                     |                        |                  | 0.4  | v    |

| OW-VOLTAGE MONITORING INPUTS                       |                                       |                                                                 |                        |                  |      |      |

| Voltage Range                                      | V <sub>3MON</sub> , V <sub>4MON</sub> | 1                                                               | -0.3                   |                  | 5.5  | V    |

| Input Resistance                                   | RIN_V1MON, RIN_V2MON                  |                                                                 | 010                    | 50               | 0.0  | KΩ   |

| V3MON, V4MON                                       |                                       |                                                                 |                        |                  |      | 1022 |

| V <sub>3MON</sub> Threshold Tolerance              | $\Delta V_{3MON}$                     | T <sub>A</sub> = 25°C                                           | -1.5                   |                  | +1.5 | %    |

| (Figure 6 and Table 5a)                            |                                       | $T_{A} = -40^{\circ}$ C to 85°C                                 | -2                     |                  | +2.7 | %    |

| gare o ana rubie bay                               |                                       | $T_A = -40^{\circ}$ C to 125°C                                  | -3                     |                  | +3.5 | %    |

| V <sub>3MON</sub> Hysteresis                       | V <sub>3 HYSTERESIS</sub>             |                                                                 |                        | 1.5              |      | %    |

# Preliminary Technical Data

| Parameter                                | Symbol                    | Conditions                                           | Min                    | Typ1                | Max                   | Ur |

|------------------------------------------|---------------------------|------------------------------------------------------|------------------------|---------------------|-----------------------|----|

| V <sub>4MON</sub> Threshold Tolerance    | $\Delta V_{4MON}$         | $T_A = 25^{\circ}C$                                  | -2.5                   |                     | +2.5                  | %  |

| (Figure 7 and Table 5a)                  |                           | $T_A = -40^{\circ}C$ to $85^{\circ}C$                | -3                     |                     | +3                    | %  |

|                                          |                           | $T_{A} = -40^{\circ}C$ to 125°C                      | -3.5                   |                     | +3.5                  | %  |

| V <sub>4MON</sub> Hysteresis             | V <sub>4</sub> hysteresis |                                                      |                        | 6                   |                       | %  |

| Reset Hold Time Tolerance                | $\Delta t_{RS}$ Hold      | Does not apply to codes 0x6 and                      | -10                    |                     | +10                   | %  |

| (Figures 6, 7, and Table 6a)             |                           | 0x7                                                  |                        |                     |                       | ,  |

| V <sub>3,4MON</sub> -to-RESET Delay      | t <sub>RS DELAY</sub>     |                                                      |                        | 70                  |                       | μs |

| RESET Output Voltage                     | VoH                       |                                                      | V <sub>3MON</sub> -1.5 |                     |                       | v  |

|                                          |                           | $V_{3MON} \ge 4.38V$ , $I_{SOURCE} = 120uA$          | 0.8xV3MON              |                     |                       | v  |

|                                          |                           | $2.7V < V_{3MON} \le 4.38V$ , $I_{SOURCE} = 30uA$    |                        |                     |                       |    |

|                                          |                           | $2.3V < V_{3MON} \leq 2.7V, I_{SOURCE} = 20uA$       | 0.8xV <sub>змол</sub>  |                     |                       | V  |

|                                          |                           | $1.8V \le V_{3MON} \le 2.3V$ , $I_{SOURCE} = 8uA$    | 0.8xV <sub>3МОN</sub>  |                     |                       | V  |

|                                          | V <sub>OL</sub>           | $V_{3MON} > 4.38V$ , $I_{SINK} = 3.2mA$              |                        |                     | 0.4                   | V  |

|                                          |                           | $V_{3MON} < 4.38V$ , $I_{SINK} = 1.2mA$              |                        |                     | 0.3                   | V  |

| RESET Output Short-Circuit               | ISOURCE                   | $\overline{\text{RESET}} = 0, V_{3MON} = 5.5V$       |                        |                     | 800                   | μA |

| Current <sup>3</sup>                     |                           |                                                      |                        |                     | 400                   |    |

|                                          |                           | $\overline{\text{RESET}} = 0, V_{3MON} = 3.6V$       |                        |                     | 400                   | μA |

| Glitch Immune Time                       | t <sub>GLITCH</sub>       |                                                      |                        | 50                  |                       | μs |

| V <sub>40UT</sub> Maximum Output         | V <sub>4OUT_MAX</sub>     | Open Drain                                           |                        |                     | 5.5                   | v  |

| V <sub>40UT</sub> Propagation Delay      | tv4OUT_Delay              |                                                      |                        | 70                  |                       | μs |

| V <sub>40UT</sub> Maximum Frequency      | f <sub>v4OUT</sub>        | Apply to RESET disabled only                         |                        | 10                  |                       | Kŀ |

| WDI (WATCHDOG INPUT)                     |                           |                                                      | 1                      |                     |                       | 1  |

| WDI Programmable-Timeout<br>Tolerance    | $\Delta t_{WD}$           |                                                      | -10                    |                     | +10                   | %  |

| (Figure 8 and Table 6a)                  |                           |                                                      |                        |                     |                       |    |

| WDI Pulse Width                          | t <sub>WDI</sub>          |                                                      | 50                     |                     |                       | ns |

| Watchdog-Initiated RESET Pulse Width     | t <sub>WDR</sub>          | When no WDI                                          |                        | t <sub>wD</sub> /50 |                       | m  |

| Watchdog-Initiated SHDN                  | twd_shdn                  | When no WDI activity $> 4 t_{WD}$                    |                        | 1                   |                       | s  |

| WDI Input Voltage                        | VIL_WD                    |                                                      |                        |                     | 0.3xV <sub>3МОN</sub> | V  |

|                                          | V <sub>IH_WD</sub>        |                                                      | $0.7 x V_{3MON}$       |                     |                       | V  |

| WDI Input Current                        |                           | WDI = $V_{3MON}$ , time average                      |                        |                     | 160                   | μA |

|                                          |                           | WDI = 0, time average                                | -20                    |                     |                       | μA |

| MR (MANUAL RESET) INPUT                  | -                         |                                                      |                        |                     |                       |    |

| MR Input Voltage                         | V <sub>IL_MR</sub>        |                                                      |                        |                     | 0.3*V <sub>3MON</sub> | V  |

|                                          | V <sub>IH_MR</sub>        |                                                      | 0.7*V <sub>3MON</sub>  |                     |                       | V  |

| MR Pulse Width                           | t <sub>MR</sub>           |                                                      | 1                      |                     |                       | μs |

| MR Deglitching                           | t <sub>MR_GLITCH</sub>    |                                                      |                        | 100                 |                       | ns |

| MR -to-Reset Delay                       | t <sub>MR_DELAY</sub>     |                                                      |                        | 1                   |                       | μs |

| MR Pullup Resistance (internal to V3MON) |                           |                                                      |                        | 50                  |                       | κΩ |

| Reset Hold-Time Tolerance                | $\Delta t_{ m RS}$ hold   | Do not apply to codes 0x6 and 0x7                    | -10                    |                     | +10                   | %  |

| (Figure 9 and Table 6a)                  |                           |                                                      |                        |                     |                       |    |

| SERIAL INTERFACES                        |                           |                                                      |                        |                     |                       |    |

| Input Logic High (SCL, SDA) <sup>4</sup> | VIH                       | External Rpull-up = $2.2k\Omega$                     | 2.0                    |                     | 5.5                   | V  |

| Input Logic Low (SCL, SDA)               | VIL                       | External Rpull-up = $2.2k\Omega$                     | 0                      |                     | 0.8                   | v  |

| Output Logic High (SDA)                  | V <sub>он</sub>           | $V_{RAIL} = 3.3V$ , External Rpull-up = $2.2k\Omega$ | 3.0                    |                     | 3.3                   | V  |

| Output Logic Low (SDA)                   | Vol                       | $V_{RAIL} = 3.3V$ , External Rpull-up = $2.2k\Omega$ | 0                      |                     | 0.4                   | v  |

| Input Capacitance                        | Cı                        |                                                      |                        | 5                   |                       | pł |

| POWER SUPPLY                             |                           |                                                      | •                      |                     |                       |    |

|                                          |                           |                                                      |                        |                     |                       | V  |

## AD5100

| Parameter                                                                                                             | Symbol           | Conditions                                        | Min | Typ <sup>1</sup> | Мах | Unit |

|-----------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------|-----|------------------|-----|------|

| Sleep Mode Supply Current                                                                                             | ISLEEP_V1MON     | $V_{2MON} = 0 V$                                  |     |                  | 10  | μΑ   |

| Active Mode Supply Current                                                                                            | POWER_V1MON      | $V_{2MON} = 12 V$                                 |     |                  | 3   | mA   |

|                                                                                                                       |                  | V <sub>2MON</sub> Edge Triggered Mode<br>Selected |     |                  | 3   | mA   |

| Device Power On Threshold                                                                                             | V2MON,IH         |                                                   | 2.2 |                  |     | V    |

|                                                                                                                       | V2MON,IL         |                                                   |     |                  | 0.4 | V    |

| Device Power Up V2MON Minimum                                                                                         |                  |                                                   |     |                  |     |      |

| Pulse Width (Figure 14)                                                                                               | tv2mon_pw        |                                                   | 4   |                  |     | ms   |

| Device Power Down Delay                                                                                               |                  | V2MON < 0.4V (Normal Mode)                        |     | 2                |     | S    |

|                                                                                                                       |                  | I2C Initiated Power Down                          |     | 10               |     | μs   |

| OTP Supply Voltage <sup>6</sup>                                                                                       | V <sub>OTP</sub> | For OTP only                                      | 6   |                  | 6.5 | V    |

| OTP Supply Current                                                                                                    | IVOTP            | For OTP only                                      | 200 |                  |     | mA   |

| OTP Settling Time <sup>7</sup>                                                                                        | ts_otp           |                                                   |     | 12               |     | ms   |

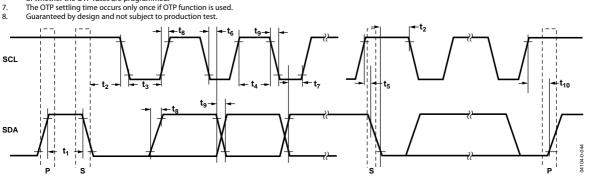

| TIMING CHARACTERISTICS 8                                                                                              |                  |                                                   |     |                  |     | •    |

| Parameter Adjustment Time                                                                                             | t <sub>s1</sub>  |                                                   |     | 1                |     | μs   |

| I2C Interface Timing                                                                                                  |                  |                                                   |     |                  |     |      |

| Characteristics                                                                                                       |                  |                                                   |     |                  |     |      |

| SCL Clock Frequency                                                                                                   | f <sub>SCL</sub> |                                                   |     |                  | 400 | KHz  |

| t <sup>BUF</sup> Bus Free Time between Start<br>and Stop                                                              | t1               |                                                   | 1.3 |                  |     | μs   |

| t <sub>HD;STA</sub> Hold Time after (Repeated)<br>START condition. After this period,<br>the first clock is generated | t <sub>2</sub>   |                                                   | 0.6 |                  |     | μs   |

| tLOW Low Period of SCL Clock                                                                                          | t <sub>3</sub>   |                                                   | 1.3 |                  |     | μs   |

| t <sub>HIGH</sub> High Period of SCL Clock                                                                            | t <sub>4</sub>   |                                                   | 0.6 |                  | 50  | μs   |

| tsu;sta Setup Time for Start<br>Condition                                                                             | t <sub>5</sub>   |                                                   | 0.6 |                  |     | μs   |

| thd;dat Data Hold Time                                                                                                | t <sub>6</sub>   |                                                   |     |                  | 0.9 | μs   |

| tsu;dat Data Setup Time                                                                                               | t <sub>7</sub>   |                                                   | 0.1 |                  |     | μs   |

| tF Fall Time of Both SDA and SCL<br>Signals                                                                           | t <sub>8</sub>   |                                                   |     |                  | 0.3 | μs   |

| t <sub>R</sub> Rise Time of Both SDA and SCL<br>Signals                                                               | t <sub>9</sub>   |                                                   |     |                  | 0.3 | μs   |

| t <sub>su;sto</sub> Setup Time for Stop<br>Condition                                                                  | t10              |                                                   | 0.6 |                  |     | μs   |

Notes: 1. 2.

Represent typical values at 25°C, V<sub>IMON</sub> = 12 V, and V<sub>2MON</sub> = 12 V. Doe<u>s not apply</u> if V<sub>2MON</sub> is a digital signal. The RESET short-circuit current is the maximum pullup current when RESET is driven low by a µP bidirectional reset pin.

3. 4.

The ACSE1<sup>®</sup> short-circuit current is the maximum pullup current when ACSE1<sup>®</sup> is driven low by a µ<sup>D</sup> bidirectional reset pin. It is typical for the SCL and SDA have resistors to be pulled up to V<sub>JMON</sub>. However, care must be taken to ensure that the minimum V<sub>H</sub> is met when the SCL and SDA are driven directly from a low voltage logic controller without pull-up resistors. Initial V<sub>JMON</sub> ON minimum remains as 2.2V but the -0.3V to 30V specifications apply afterwards. V<sub>OTP</sub> can be furnished by Factory 6V power supply, rather than on-board power supply, when performing factory programming. A 10uF tantalum capacitor is required on V<sub>OTP</sub> during operation regardless of whether the OTP fuses are programmed. The OTP settling time occurs only once if OTP function is used. Guaranteed by design and not subject to production test. 5. 6.

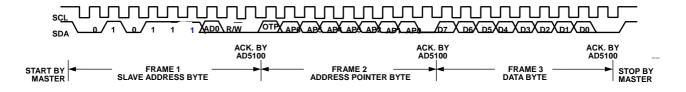

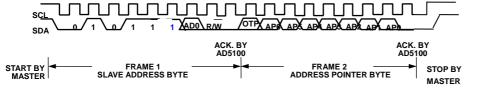

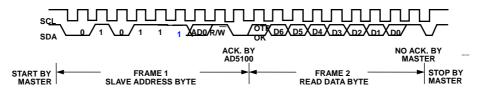

Figure 2. Digital Interface Timing Diagram

## **Absolute Maximum Ratings**

Table 3.

| Parameter                                                                                                      | Rating             |

|----------------------------------------------------------------------------------------------------------------|--------------------|

| V <sub>1MON</sub> to GND                                                                                       | −0.3 V, +33 V      |

| V <sub>2MON</sub> to GND                                                                                       | −0.3 V, +33 V      |

| V <sub>3MON</sub> to GND                                                                                       | –0.3 V, +7 V       |

| V <sub>4MON</sub> to GND                                                                                       | –0.3 V, +7 V       |

| V <sub>OTP</sub> to GND                                                                                        | –0.3 V, +7 V       |

| Digital Input Voltage to GND (MR , WDI,<br>SCL, SDA, AD0)                                                      | 0 V, +7V           |

| Digital Output Voltage to GND ( $\overline{\text{RESET}}$ , V <sub>40UT</sub> , $\overline{\text{SHDNWARN}}$ ) | 0 V, +7V           |

| Digital Output Voltage to GND (SHDN )                                                                          | 0 V, +33V          |

| Operating Temperature Range                                                                                    | −40°C to<br>+125°C |

| HBM ESD (All Pins)                                                                                             | 2KV                |

| Maximum Junction Temperature<br>(TJmax)                                                                        | 140°C              |

| Storage Temperature                                                                                            | −65°C to<br>+150°C |

| Lead Temperature (Soldering, 10 s – 30<br>s)                                                                   | 245°C              |

| Thermal Resistance Junction-to-<br>Ambient <sup>1</sup> $\theta_{JA}$                                          | 105°C/W            |

| Thermal Resistance Junction-to-Case $\theta_{JC}$                                                              | 39°C/W             |

**Preliminary Technical Data**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>1</sup> Package power dissipation =  $(T_J max - T_A) / \theta_{JA}$ .

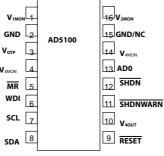

# **PIN CONFIGURATION AND FUNCTIONAL DESCRIPTION**

Figure 3a. AD5100 Pin Configuration

|     | GND     |    |

|-----|---------|----|

|     |         | 16 |

| 2   |         | 15 |

| 3   |         | 14 |

| _4_ | AD5100  | 13 |

| 5   | 7.00100 | 12 |

| 6   |         | 11 |

| _7_ |         | 10 |

| 8   |         | 9  |

Figure 3b. Recommended PCB Layout for Shielded High-Voltage Inputs

| Table 4. AD | 5100 Pi | n Function | Desc | riptions |  |

|-------------|---------|------------|------|----------|--|

|             |         |            | (    |          |  |

| Pin No. | Mnemonic          | Description                                                                                                                                         |

|---------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V <sub>1MON</sub> | High-voltage monitoring input. AD5100 internal supply is derived from V <sub>1MON.</sub>                                                            |

| 2       | GND               | Ground.                                                                                                                                             |

| 3       | VOTP              | One-time supply voltage for EPROM. Can be floating when it is not performing fuse programming                                                       |

| 4       | V <sub>3MON</sub> | Low-voltage monitoring-input                                                                                                                        |

| 5       | MR                | Manual-Reset Input. Active-low.                                                                                                                     |

| 6       | WDI               | Watch-Dog Input.                                                                                                                                    |

| 7       | SCL               | I2C Serial-Input Register Clock. If it is driven directly from a logic driver without the pull-up resistor, ensure that V <sub>H</sub> min is 3.3V. |

| 8       | SDA               | I2C Serial Data Input/Output. If it is driven direct from a logic driver without the pull-up resistor, ensure that $V_{IH}$ min is 3.3V.            |

| 9       | RESET             | $\overline{\mathrm{RESET}}$ , Push-Pull Output with rail voltage of V <sub>3MON</sub>                                                               |

| 10      | V <sub>4OUT</sub> | Open-drain output. Triggered by $V_{4MON}$                                                                                                          |

| 11      | SHDNWARN          | Shutdown Warning. Active-Low, Open-drain output.                                                                                                    |

| 12      | SHDN              | Shutdown output. Push-Pull Output with selectable rail voltage of $V_{1MON}$ or $V_{REG}$ . 30V maximum                                             |

| 13      | AD0               | I2C Slave-Address Configuration.                                                                                                                    |

| 14      | V <sub>4MON</sub> | Low-voltage monitoring Input.                                                                                                                       |

| 15      | GND/NC            | Ground/No Connect. Can be grounded or left floating but do not connect to any other potentials.                                                     |

| 16      | V <sub>2MON</sub> | High-voltage monitoring input. It is also the internal-supply-voltage enabling input.                                                               |

# **Preliminary Technical Data**

| 5                                    |                                      | , ,                                  | 5                                                    | -                              |                                |

|--------------------------------------|--------------------------------------|--------------------------------------|------------------------------------------------------|--------------------------------|--------------------------------|

| V <sub>1MON</sub><br>OV<br>Threshold | V <sub>1MON</sub><br>UV<br>Threshold | V <sub>2MON</sub><br>ON<br>Threshold | V <sub>2MON</sub><br>OFF<br>Threshold                | V <sub>змоn</sub><br>Threshold | V <sub>4MON</sub><br>Threshold |

| 7.92                                 | 6.00                                 | 3.00                                 | 3.00                                                 | 2.32                           | Disabled*                      |

| 9.00                                 | 6.49                                 | 3.30                                 | 3.30                                                 | 2.64                           | 0.86                           |

| 9.90                                 | 6.95                                 | 4.50                                 | 4.50                                                 | 2.93                           | 1.15                           |

| 11.00                                | 7.47                                 | 4.77                                 | 4.77                                                 | 3.10                           | 1.37                           |

| 12.00                                | 7.92                                 | 6.00                                 | 6.00                                                 | 4.36*                          | 1.43                           |

| 13.20                                | 8.43*                                | 6.49                                 | 6.49                                                 | 4.65                           | 1.66                           |

| 14.14                                | 9.00                                 | 6.95                                 | 6.95*                                                | 4.75                           | 2.30                           |

| 15.23                                | 9.43                                 | 7.47*                                | 7.47                                                 | 4.97                           | 3.10                           |

| 15.84                                | 9.90                                 | 7.92                                 | 7.92                                                 | Reserved                       | Reserved                       |

| 17.22                                | 10.42                                | 8.43                                 | 8.43                                                 | Reserved                       | Reserved                       |

| 18.00*                               | 11.00                                | 9.00                                 | 9.00                                                 | Reserved                       | Reserved                       |

| 18.86                                | 11.65                                | 9.43                                 | 9.43                                                 | Reserved                       | Reserved                       |

| 19.80                                | 12.00                                | 9.90                                 | 9.90                                                 | Reserved                       | Reserved                       |

| 22.00                                | 12.38                                | 15.23                                | 15.23                                                | Reserved                       | Reserved                       |

| 24.75                                | 13.20                                | 19.80                                | 19.80                                                | Reserved                       | Reserved                       |

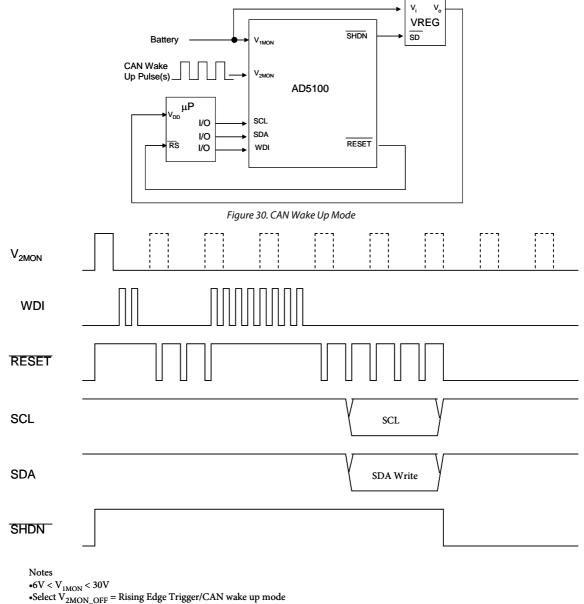

| 28.29                                | 13.66                                | 24.75                                | Rising Edge<br>Trigger/Pseudo<br>CAN Wake Up<br>Mode | Reserved                       | Reserved                       |

Table 5a. Available Programmable-Threshold at  $T_A = 25 \degree C$  (All values are typical ratings; see Table 2 for tolerances)

\* Default.  $V_{1MON_OV}$  must be >  $V_{1MON_UV}$ .  $V_{2MON_OFF}$  will be ignored if >  $V_{2MON_ON}$  but  $V_{2MON_OFF}$  cannot be =  $V_{2MON_ON}$ .

#### Table 5b. Look Up Table of Programming Code versus Typical Thresholds Shown in Table 5a

| Co  | le V <sub>1MON</sub><br>OV<br>Thresho | UV      | V <sub>2MON</sub><br>ON<br>d Thresho | V <sub>2MON</sub><br>OFF<br>Id Threshold             | V <sub>3MON</sub><br>Threshold | V <sub>4MON</sub><br>Threshold |

|-----|---------------------------------------|---------|--------------------------------------|------------------------------------------------------|--------------------------------|--------------------------------|

| 000 | 00 18.00 <sup>*</sup>                 | * 8.43* | 7.47*                                | 6.95*                                                | 4.36*                          | Disabled*                      |

| 000 | 18.86                                 | 7.92    | 6.95                                 | 7.47                                                 | 4.65                           | 0.86                           |

| 00  | 0 15.84                               | 9.43    | 6.49                                 | 6.00                                                 | 4.75                           | 1.15                           |

| 00  | 1 17.22                               | 9.00    | 6.00                                 | 6.49                                                 | 4.97                           | 1.37                           |

| 010 | 0 24.75                               | 6.49    | 4.77                                 | 4.50                                                 | 2.32                           | 1.43                           |

| 010 | 28.29                                 | 6.00    | 4.50                                 | 4.77                                                 | 2.64                           | 1.66                           |

| 01  | 0 19.80                               | 7.47    | 3.30                                 | 3.00                                                 | 2.93                           | 2.30                           |

| 01  | 1 22.00                               | 6.95    | 3.00                                 | 3.30                                                 | 3.10                           | 3.10                           |

| 100 | 9.90                                  | 12.38   | 24.75                                | 19.80                                                | Reserved                       | Reserved                       |

| 100 | 01 11.00                              | 12.00   | 19.80                                | Rising Edge<br>Trigger/Pseudo<br>CAN Wake Up<br>Mode | Reserved                       | Reserved                       |

| 10  | 0 7.92                                | 13.66   | 15.23                                | 9.90                                                 | Reserved                       | Reserved                       |

| 10  | 1 9.00                                | 13.20   | 9.90                                 | 15.23                                                | Reserved                       | Reserved                       |

| 11( | 00 14.14                              | 10.42   | 9.43                                 | 9.00                                                 | Reserved                       | Reserved                       |

| 11( | 15.23                                 | 9.90    | 9.00                                 | 9.43                                                 | Reserved                       | Reserved                       |

| 11  | 0 12.00                               | 11.65   | 8.43                                 | 7.92                                                 | Reserved                       | Reserved                       |

| 11  | 1 13.20                               | 11.00   | 7.92                                 | 8.43                                                 | Reserved                       | Reserved                       |

|     |                                       |         |                                      |                                                      |                                |                                |

200\*

## AD5100

| Table 6a. Ava | iilable Programma             | ble Hold Time a                | nd Delay (All va              | lues are typical               | ratings; see Tab             | le 2 for tolera         | nces) |

|---------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|------------------------------|-------------------------|-------|

|               | t <sub>1SD_HOLD</sub><br>(ms) | t <sub>1SD_DELAY</sub><br>(ms) | t <sub>2SD_HOLD</sub><br>(ms) | t <sub>2SD_DELAY</sub><br>(ms) | t <sub>rs_HOLD</sub><br>(ms) | t <sub>wD</sub><br>(ms) |       |

|               | 0.07                          | 0.07                           | 0.07                          | 0.07                           | 0.1                          | 100                     |       |

|               | 20                            | 50                             | 10*                           | 50                             | 1                            | 250                     |       |

|               | 40                            | 100                            | 20                            | 100*                           | 15                           | 500                     |       |

|               | 60                            | 200                            | 30                            | 200                            | 30                           | 750                     |       |

200\*

1500\*

\* Default

Table 6b. Look Up Table of Programming Code versus Typical Timings Shown in Table 6a

1200\*

| Code      | t <sub>1SD_HOLD</sub><br>(ms) | t <sub>1SD_DELAY</sub><br>(ms) | t <sub>2SD_HOLD</sub><br>(ms) | t <sub>2SD_DELAY</sub><br>(ms) | t <sub>rs_HOLD</sub><br>(ms) | t <sub>wD</sub><br>(ms) |

|-----------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|------------------------------|-------------------------|

| 000       | 200*                          | 1200*                          | 10*                           | 100*                           | 200*                         | 1500*                   |

| 001       | 150                           | 1000                           | 20                            | 50                             | 150                          | 2000                    |

| 010       | 100                           | 800                            | 30                            | 200                            | 100                          | 1250                    |

| 011       | 80                            | 400                            | 40                            | 400                            | 50                           | 1000                    |

| 100       | 60                            | 200                            | 50                            | 800                            | 30                           | 750                     |

| 101       | 40                            | 100                            | 100                           | 1000                           | 15                           | 500                     |

| 110       | 20                            | 50                             | 200                           | 1200                           | 1                            | 250                     |

| 111       | 0.07                          | 0.07                           | 0.07                          | 0.07                           | 0.1                          | 100                     |

| 6 Dafault |                               |                                |                               |                                |                              |                         |

\* Default

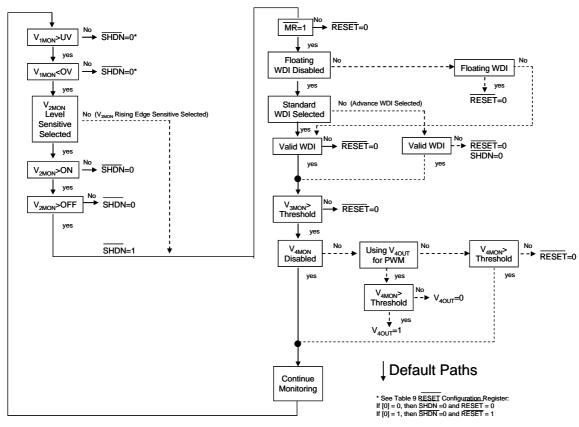

### THEORY OF OPERATION

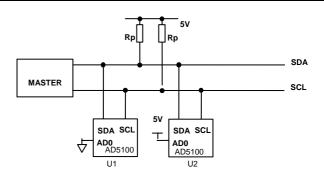

The AD5100 is a Programmable System Management IC that has four channels of monitoring inputs. Two inputs have high voltage (30V) capability. For example if the AD5100 is used in the automotive application, the V<sub>1MON</sub> (Monitoring Input 1) should be the battery and the V<sub>2MON</sub> should either be the ignition switch or the pseudo CAN bus wake up signal input. Two other inputs, V<sub>3MON</sub> and V<sub>4MON</sub>, are low voltage for 0.9V, 1.8V, 2.5V, 3.3V, or 5V monitoring. The two high voltage inputs control the shutdown signal, <u>SHDN</u>, while the two low voltage inputs control the reset signal, <u>RESET</u>. The <u>SHDN</u> and <u>RESET</u>

are both disabling functions for the external devices. The differences are output levels and driving capabilities that will be described later. In some cases the  $\overline{SHDN}$  and  $\overline{RESET}$  may be used interchangeably. The WDI (Watchdog) and  $\overline{MR}$  (Manual Reset) inputs also control  $\overline{RESET}$  output for external digital processor. Figure 4 shows the general flow chart and Table 7 summarizes the AD5100 functions and features.

Figure 4. General Flow Chart

#### Table 7. AD5100 Functions and Features

| Input             | Monitoring<br>Range | Shutdown<br>Control | Reset<br>Cont<br>rol | Fault<br>Dete<br>ction | Functions and Features | If Not Used                          |

|-------------------|---------------------|---------------------|----------------------|------------------------|------------------------|--------------------------------------|

| V <sub>1MON</sub> | 6 – 30 V            | $\checkmark$        | $\checkmark$         | $\checkmark$           | Over/Under Voltage     | Does not apply                       |

| $V_{2MON}$        | 3 – 30 V            | $\checkmark$        | $\checkmark$         | $\checkmark$           | On/Off Voltage         | Tie to V <sub>1MON</sub> , Min Input |

|                   |                     |                     |                      |                        | CAN Bus Wake Up        |                                      |

| V <sub>3MON</sub> | 2.5 – 5.0 V         |                     | $\checkmark$         | $\checkmark$           |                        | Connect to VOTP and                  |

|                   |                     |                     |                      |                        |                        | Threshold to Minimum                 |

| V <sub>4MON</sub> | 0.9 – 3.3 V         |                     |                      |                        | Additional Output      | Select Disable in Threshold          |

| WDI               | 0 – 5 V             |                     | $\checkmark$         |                        | Standard, Advance, or  | Leave Floating                       |

|                   |                     |                     |                      |                        | Watchdog Selectable    |                                      |

<u>MR</u> 0 – 5 V

**Monitoring Inputs**

V<sub>1MON</sub>

$V_{1MON}$  is a high-voltage monitoring input that controls the SHDN and RESET functions of the external devices. In addition, it also provides a shutdown warning to the system.  $V_{1MON}$  monitors inputs from 6V to 30V. It has a 16-level programmable over-voltage, under-voltage (OV,UV) shutdown threshold with an 8-step 0.05ms-200ms shutdown hold time and 0.05ms-1200ms shutdown delay. The shutdown hold time means that the shutdown of the external device is held until the programmed-time is reached. On the other hand, the shutdown delay means that shuting down the external device is delayed until the programmed-time is reached.

$\sqrt{}$

The OV threshold chosen must be greater than the UV threshold. When the shutdown is triggered either because the input has reached OV or UV threshold, such fault condition will be temporarily recorded in the Fault Detection Register. The SHDNWARN output will transition low for signaling before shutdown occurs. The occurance of Shutdown is

<u>Highes</u>t Prority on Other Inputs

section.

Leave Floating

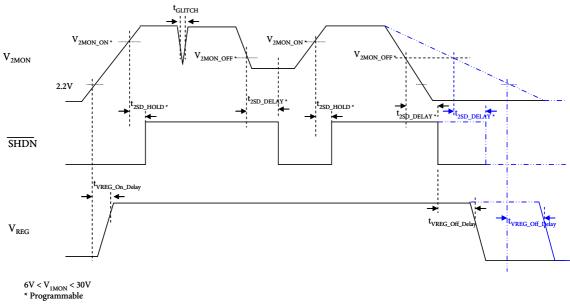

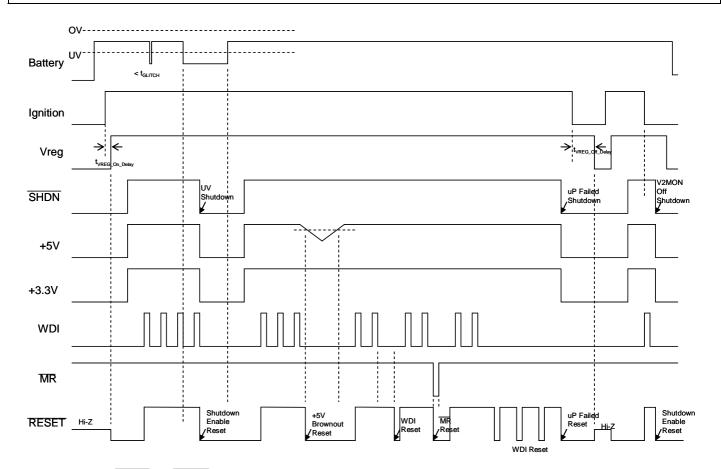

depending on how long the shutdown programmed-delay is set relative to the SHDNWARN propagation delay, this feature attempts to allow the system to finish any critical house keeping tasks before shuting down the external device. The V<sub>1MON</sub>, shutdown, and shutdown warning timing diagrams are shown in Figure 5. The ranges of OV and UV Thresholds are shown in Table 5a and the programming codes of the selected-thresholds are found in Table 5b. The defaulted OV threshold is 18.00V and UV threshold is 8.43V. Simarily, the ranges of shutdown hold and delay times are shown in Table 6a and the programming codes of the selected-timings are found in Table 6b. The defaulted shutdown hold time is 200ms delay time is 1200ms. The voltage at  $V_{1MON}$  provides the power for the AD5100 but valid signal at V<sub>2MON</sub> must be present before the internal V<sub>REG</sub> starts operation. Details will be explained in the power

VIMON VIMON V2MON V2MON

\* = Programmable #: The duration of the  $t_{MIN}$  must be shorter than  $t_{VREG_Off_Delay}$  or else the AD5100 will be powered off

Figure 5.  $V_{1MON}$  and  $V_{2MON}$  Shutdown Timing Diagrams (Note RESET follows SHDN ).

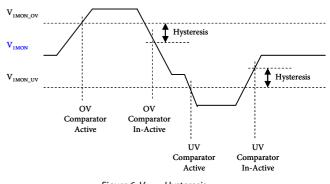

The  $V_{1MON}$  pin is monitored by two comparators, one for over-voltage, and one for under-voltage detection. Both are designed with 1.5% hysteresis.

indicating an OV condition has occurred. Due to hysteresis, the  $V_{1MON}$  input must be brought below the programmed OV threshold by 1.5% before the comparator will be in-active, indicating the OV condition has gone away, see Figure 6.

When the V<sub>1MON</sub> input drops below the programmed UV threshold, the comparator will become active immediately, indicating a UV condition has occurred. Similarly due to hysteresis, the V<sub>1MON</sub> input must be brought above the programmed UV threshold by 1.5% before the comparator will be in-active, indicating the UV condition has gone away. Both V1mon comparators are used (in conjunction with hold and delay timers) to control the SHDN and RESET pins. V<sub>1MON</sub> exhibits typical input resistance of  $60K\Omega$  that users should account the loading effect.

The default  $V_{1MON}$  OV and UV thresholds are 18.00V and 8.43V respectively. The default  $V_{1MON}$  Shutdown Hold time and Shutdown Delay are 200ms and 1200ms respectively. User should refer to Tables 5b and 6b if they want to program different settings.

#### V<sub>2MON</sub>

$V_{\rm 2MON}$  is a high-voltage monitoring input that controls the  $\overline{\rm SHDN}$  and  $\overline{\rm RESET}$  functions of the external devices.  $V_{\rm 2MON}$  monitors inputs from 3V to 30V. It has a 16-level programmable Turn-on, Turn-off (ON,OFF) hysteresis threshold with an 8-step 0.05ms-200ms shutdown hold time and 0.05ms-1200ms shutdown delay.

By default,  $V_{2MON}$  is level-sensitive that the ON and OFF thresholds are both monitored. The ON threshold chosen must be greater than the OFF threshold. When the shutdown function is triggered by the input reaching V<sub>2MON OFF</sub> threshold, such fault condition will be temporarily recorded in the Fault Detection Register. The SHDNWARN output will transition low for signaling before shutdown occurs. The occurance of shutdown is depending on how long the shutdown programmed-delay is set relative to the SHDNWARN propagation delay, this feature attempts to allow the system to finish any critical house keeping tasks before shuting down the external device. The V<sub>2MON</sub>, shutdown, and shutdown warning pins timing diagrams are also shown in Figure 5. The ranges of ON and OFF Thresholds are shown in Tables 5a and the programming codes of the selectedthresholds are found in Table 5b. The defaulted ON threshold is 7.47V and OFF threshold is 6.95V. Simarily, the ranges of shutdown hold and delay times are shown in Table 6a and the programming codes of the selected-timings are found in Table 6b. The defaulted shutdown hold time is 10ms and delay time is 100ms.

$V_{2MON\_OFF} \text{ will be ignored if } V_{2MON\_OFF} > V_{2MON\_ON} \text{ but } V_{2MON\_OFF} \text{ cannot be} = V_{2MON\_ON}.$

If the  $V_{2MON}$  is selected with Rising Edge Triggered, only the ON threshold is monitored and the OFF Threshold is ignored.

The voltage at  $V_{\rm 1MON}$  provides the power for the AD5100 but valid signal at  $V_{\rm 2MON}$  must be present before the internal  $V_{\rm REG}$  starts operation. Details will be explained in the power section.

### **Preliminary Technical Data**

Figure 6. V<sub>1MON</sub> Hysteresis.

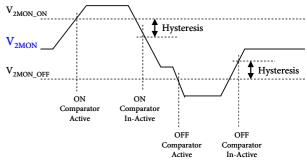

The  $V_{2MON}$  pin is monitored by 2 comparators, 1 for turn-on, and 1 for turn-off detection in the level sensitive power-up mode. Both are designed with 1.5% hysteresis. On the other hand, the turn-on monitoring comparator is used only if the rising edge trigger power-up mode is selected.

When the  $V_{2MON}$  input goes above the programmed Ton threshold, the comparator will become active immediately, indicating an OV condition has occurred. Due to hysteresis, the  $V_{2MON}$  input must be brought below the programmed threshold by 1.5% before the comparator will be in-active, indicating the OV condition has gone away, see Figure 7.

When the  $V_{2MON}$  input drops below the programmed threshold, the comparator will become active immediately, indicating a UV condition has occurred. Similarly due to hysteresis, the  $V_{2MON}$  input must be brought above the programmed threshold by 1.5% before the comparator will be in-active, indicating the UV condition has gone away.

Figure 7. V<sub>2MON</sub> Hysteresis.

$V_{\rm 2MON}$  exhibits typical input resistance of  $60 K \Omega$  that users should account the loading effect.

The default  $V_{2MON}$  ON and OFF thresholds are 7.47V and 6.95V respectively. The default  $V_{2MON}$  Shutdown Hold time and Shutdown Delay are 10ms and 100ms respectively. User should refer to Tables 5b and 6b if they want to program different settings.

# AD5100

#### V<sub>3MON</sub>

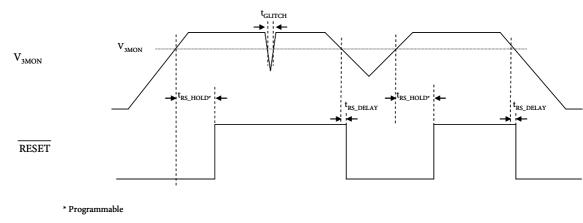

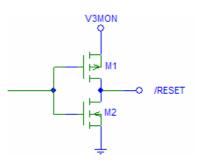

$V_{3MON}$  is a low-voltage monitoring input that controls the RESET function of an external device.  $V_{3MON}$  monitors inputs from 2.5V to 5.5V. It has an 8-step programmable reset threshold with an 8-step 0.1ms-200ms reset hold time. The reset hold time means that the reset of the external device is held until the programmed-time is reached. The  $V_{3MON}$  and reset timing diagrams are shown in Figure 8. The range of

thresholds is shown in Table 5a and the programming code of the selected-threshold is found in Table 5b. The defaulted monitoring threshold is 4.36V. Similarly, the range of reset hold time is shown in Tables 6a and the programming code of the selected-timing is found in Table 6b. The defaulted reset hold time is 200ms.

Figure 8.  $V_{3MON} \overline{RESET}$  Timing Diagrams

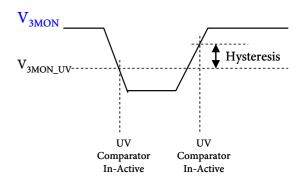

The V<sub>3MON</sub> pin is monitored by a comparator to detect an under-voltage condition. It is designed with 1.5% hysteresis. When the V<sub>3MON</sub> input drops below the programmed UV threshold, the comparator will become active immediately, indicating a UV condition has occurred. Due to hysteresis, the V<sub>3MON</sub> input must be brought above the programmed UV threshold by 1.5% before the comparator will be in-active, indicating the UV condition has gone away, see Figure 9. The V<sub>3MON</sub> comparator is used (in conjunction with a hold timer) to control the RESET pin.

$V_{3MON}$  exhibits typical input resistance of 50K $\Omega$  that users should account the loading effect.

The  $\overline{\text{MR}}\,$  input has an internal resistor pull-up to  $V_{3\text{MON}}.$  The  $\overline{\text{RESET}}\,$  output are push-pull configured between  $V_{3\text{MON}}$  and GND.

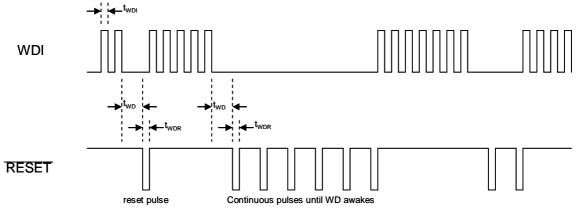

#### V<sub>4MON</sub>

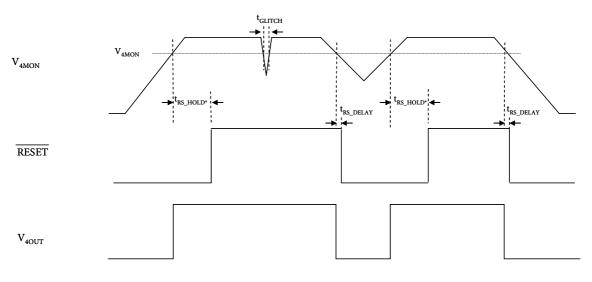

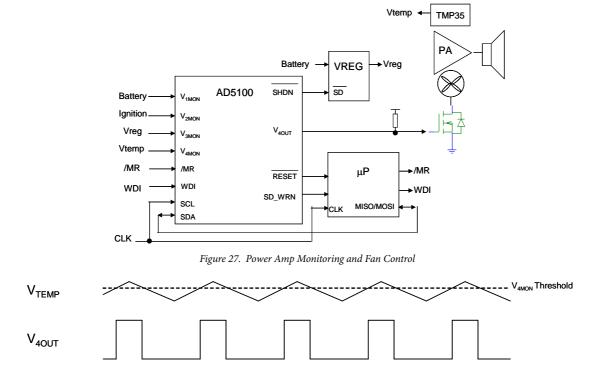

$\frac{V_{4MON}}{RESET} \ \ is the lowest voltage monitoring input that controls the RESET function of an external device or provides a comparator output, <math display="inline">V_{40UT}$ .  $V_{4MON}$  monitors input from 0.9V to 3.3V. It has an 8-step programmable reset threshold with an 8-step 0.1ms to 200ms reset hold time. The  $V_{4MON}$ , reset, and  $V_{40UT}$  timing diagrams are shown in Figure 10. The range of

Figure 9.  $V_{3MON}$  Hysteresis. The default  $V_{3MON}$  threshold is 4.36V. User should refer to Table 5b if they want to program different setting.

thresholds is shown in Table 5a and the programming code of the selected-threshold is found in Tables 5b. The defaulted monitoring threshold is Disabled. Similarly, the range of reset hold time is shown in Tables 6a and the programming code of the selected-timing is found in Table 6b.

•Programmable

Most Applications using  $\rm V_{4OUT}$  require disabling of  $\rm V_{4MON}$  triggered reset

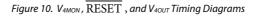

The V<sub>4MON</sub> pin is monitored by a comparator to detect an under-voltage condition. It is designed with 6% hysteresis. When the V<sub>4MON</sub> input drops below the programmed UV threshold, the comparator will become active immediately, indicating a UV condition has occurred. Due to hysteresis, the V<sub>4MON</sub> input must be brought above the programmed UV threshold by 6% before the comparator will be in-active, indicating the UV condition has gone away, See Figure 11. The V<sub>4MON</sub> comparator is used to control the V<sub>4OUT</sub> pin and also (in conjunction with a hold timer) to control the RESET pin.

$V_{\rm 4MON}$  exhibits typical input resistance of  $50 K \Omega$  that users should account the loading effect.

The default  $V_{4\text{MON}}$  is Disabled. User should refer to Table 5b if they want to program a different setting.

# AD5100

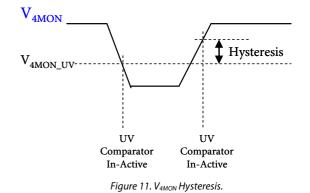

#### Watchdog Input

The Watch-Dog Input (WDI) circuit attempts to reset the system to a known good state if a software or hardware glitch renders the system processor inactive for a duration that is longer than the timeout period. There is an 8-step programmable timeout period from 100ms to 2000ms. The watchdog circuit is independent of the CPU clock that the watchdog is monitoring.

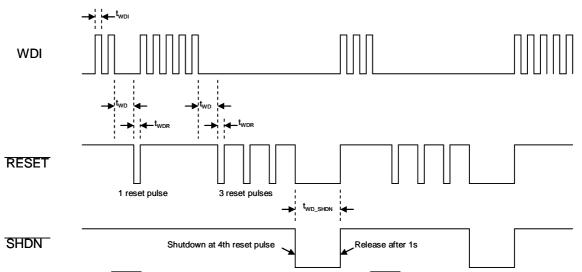

Watchdog is disabled during power-up. WDI starts monitoring once the RESET is high. Unique to AD5100, it

provides a Standard or Advance Watchdog monitoring function. In the defaulted Standard Watchdog mode, if WDI remains either high or low for longer than the timeout period, a reset pulse is generated in an attempt to allow the system processor to re-establish the WDI signal. The reset pulses continue indefinitely until a valid watchdog signal, a rising or falling edge signal at the WDI, is received. The internal watchdog timer clears whenever reset is asserted. The Standard WDI and RESET timing diagrams are shown in Figure 12.

Figure 12. Standard Watchdog – Pulsing Reset Until Watchdog Awakes.

On the other hand, the AD5100 can be programmed to an Advance Watchdog mode such that when the watchdog remains inactive longer than three times the watchdog timeout period, at the forth time the SHDN and RESET will be

asserted and released after 1 second. These actions repeat indefinitely, unless it is interferred by the user, if the processor is not responding. The Advance WDI and RESET timing diagrams are shown in Figure 13.

Figure 13. Advance Watchdog – SHDN Asserted After Three Trials of Reseting the Watchdog. SHDN Released After 1 second and the cycle repeats.

The range of Watchdog Timeout is shown in Table 6a and the programming code of the selected-timeout is found in Table 6b. The default timeout is 1500ms. If WDI is floating, the watchdog is disabled by default. However, floating watchdog can be enabled through I2C

programming such that a broken WDI connection or any unusual condition that makes WDI float will trigger the reset. Enabling or disabling floating WDI can be changed dynamically provided that the OTP fuse of such function is not programmed or the OTP overriden function is selected.

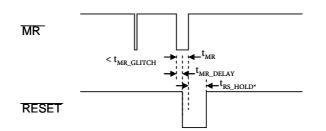

### **Manual Reset**

Manual Reset  $\overline{\text{MR}}$  is active low and it has an internal pull-up resistor to V<sub>3MON</sub>.  $\overline{\text{MR}}$  can be driven from a CMOS logic signal. The  $\overline{\text{MR}}$  and  $\overline{\text{RESET}}$  timing diagrams are shown in

**Preliminary Technical Data**

The default Watchdog Timeout is 1500ms. User should refer to Table 6b if they want to program a different setting.

Figure 14.  $\overline{\text{MR}}$  has the highest priority in triggering the  $\overline{\text{RESET}}$  over any other monitoring inputs.

•Programmable

Figure 14. Manual Reset Timing Diagrams

### Outputs

#### Shutdown Generator

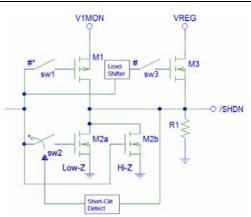

The shutdown output,  $\overline{SHDN}$ , is triggered by the abnormal inputs of  $V_{1MON}$  or  $V_{2MON}$ . It can also be the result of a failed watchdog input.  $\overline{SHDN}$  control can also be asserted low by users through I2C programming at anytime.

To be explicit, the shutdown generator asserts a logic-low SHDN signal based on the following conditions:

- 1. During power-up.

- 2. When  $V_{1\text{MON}}$  goes over or under the threshold, Figure 5.

- When V<sub>2MON</sub> is below the turn-on threshold during the rising edge or the turn-off threshold during the falling edge in the default level sensitive mode, Figure 5.

- 4. When the external monitoring processor cannot issue the necessary WDI signal and an Advanced WDI mode is selected, Figures 8 and 9.

- 5. I2C programmed-shutdown.

The SHDN signal is released after the programmable hold time. The SHDN output is push-pull configured with I<sup>2</sup>C selectable rail voltage of either V<sub>1MON</sub> in default or internal V<sub>REG</sub>. Figure 15 shows the SHDN output configurations, Pulldown resistor R1 ensures SHDN is pulled to ground when the AD5100 is not powered. When AD5100 is powered, M2a and M2b are both on. M2a has relatively lower impedance than M2b and R1 that the SHDN remains low at shutdown. When the AD5100 settles, sw1 will be on. M1 is stronger than M2a that SHDN will be pulled to the rail that makes AD5100 out of the shutdown mode.

The AD5100 is likely be used to monitor and control power regulators in some applications where some regulators have the input and enable pins next to each other in fine pitch that may pose reliability concern under some abnormal conditions. To prevent this may happen, the AD5100 shutdown output features a smart-load detection that ensures the shutdown to respond for maximum protection. For example, if the car battery has not been started for an extensive period of time and a resistive dendrite may have formed across the SHDN and the battery terminal (V1MON), the dendrite will be blown immediately as the M2a is designed with adequate current sinking capability and remains in the on position to offer such protection. In another situation where the SHDN pin may be hard-shorted to any sub-30V source, the short-circuit detector will open sw2 and therefore limit the current by the high impedance M2b.

Figure 15. Shutdown Output.  $# = l^2C$  Selectable, \* = Default.

### **Reset Generator**

The Reset output,  $\overline{\text{RESET}}$ , is triggered by the abnormal input of V<sub>3MON</sub> or V<sub>4MON</sub>.  $\overline{\text{RESET}}$  activation can also be the result of the processor that is not generating the proper watchdog signal or the Manual Reset is triggered.

To be explicit, the Reset generator asserts a logic-low  $\overline{\text{RESET}}$  signal based on the following conditions

- 1. During power up

- 2. When  $V_{3MON}$  drops below the threshold, Figure 8.

- 3. When  $V_{4MON}$  drops below the threshold, Figure 10.

- 4. When SHDN output is asserted, Figures 5 and 13.

- 5. When the external monitoring processor cannot issue the necessary WDI signal, Figures 12 and 13.

- 6. When  $\overline{\text{MR}}$  is asserted, Figure 14.

The  $\overline{\text{RESET}}$  signal is asserted and maintained except when it is triggered by the WDI that will be described in the watchdog section. The  $\overline{\text{RESET}}$  signal is released after the programmable hold time.

As shown in Figure 16, The  $\overline{\text{RESET}}$  output is push-pull configured with the the rail voltage of V<sub>3MON</sub>.

Figure 16. Reset Output.

### Fault Detection with Shutdown Warning

An early shutdown warning is available for the system processor to identify the source of failure and take appropriate action before shuting down the external devices. Whenever the voltage at  $V_{1MON}$  is detected as over-voltage or under-voltage, or the voltage at  $V_{2MON}$  falls below the threshold, SHDNWARN outputs a logic 0. If the processor sees a logic-low on this pin, the processor may issue an I2C read command to identify the cause of failure reported in the Fault Detect/Status Register. The processor may store the information in the external EEPROM as a record of failure history.

### V40UT

$V_{\rm 400T}$  is an open-drain output triggered by  $V_{\rm 4MON}$  wth minimum propogation delay and the programmable delay does not apply.  $V_{\rm 400T}$  can be used as a PWM control over an external device or used as a monitoring signal. Most applications using  $V_{\rm 400T}$  require disabling  $V_{\rm 4MON}$  triggered reset with an I2C command.

#### **Power Requirements**

#### **Internal Power**

The AD5100 internal power  $V_{REG}$  is derived from  $V_{1MON}$  and  $V_{2MON}$  is used to turn AD5100 on and off with a different behavior depending on the  $V_{2MON}$  monitoring mode selection. By default, in the  $V_{2MON}$  level sensitive mode, the AD5100 turns on when the voltage at  $V_{2MON}$  rises above the logic threshold  $V_{2MON,ON}$ , When  $V_{2MON}$  falls below the logic

threshold  $V_{2MON_OFF}$ , AD5100 will trun off 2 seconds after  $\overline{SHDN}$  is deasserted. Note that AD5100 requries 5 us to start up and that  $V_{1MON}$  must be applied before  $V_{2MON}$ . The extension of the AD5100 turn-off attempts to allow the system to complete any housekeeping tasks before the system is powered off. Figure 17 shows the defaulted  $V_{2MON}$  and  $V_{REG}$ waveforms.

If the Pulse-Sensitive  $V_{\rm 2MON}$  Mode is selected instead, the AD5100 will not turn off when  $V_{\rm 2MON}$  returns to a logic low. In this mode, once the part has been powered on, it can only

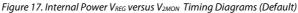

#### Votp

A 6V supply voltage is needed only during OTP fuse programming. This voltage should be provided by an external source during factory programming and should have 6V/200mA driving capability. The OTP programming duration depends on the numbers of programming fuses with maximum duration of 10ms. V<sub>OTP</sub> is not required for normal operation. The V<sub>OTP</sub> has dual functions, it is used for programming the non-volatile memory fuse arrays as well as serving as a compensation network for internal power stability. As a result, a bypass capacitor must be connected at V<sub>OTP</sub> pin at all times. A low ESR 10uF tantalum capacitor is recommended. be power-down by an I2C power down instruction or by eliminating the supply on  $V_{1MON}$  pin. This feature is for the applications that use a wake up signal.

Figure 18. Power Supply Requirement

AD5100 achieves the OTP function through blowing internal fuses. Users should always apply the 6 V one-time program voltage requirement at the first fuse programming attempt. Failure to comply with this requirement may lead to a change in the fuse structures, rendering programming inoperable.

Care should be taken when SCL and SDA are driven from a low voltage logic driver.

Poor PCB layout introduces parasitic inductance that may affect the fuse programming voltage droop. Therefore, it is mandatory that a 10 $\mu$ F tantalum capacitor be placed as close as possible to the V<sub>OTP</sub> pin. The value and the type of C2 chosen are important. It should provide both a fast response and larger supply current handling with minimum supply droop during programming, see Figure 18.

### Protection

#### Over-Current Protection

If the  $V_{\rm 1MON}$  is shorted internally in the AD5100 to GND, the short-circuit protection kicks in and limits subsequent current to 150mA in normal operation or 50mA when the  $V_{\rm OTP}$  is executed.

#### Thermal Shutdown

When the AD5100 junction temperature is near the junction temperature limit, it will automatically shutdown and cut out the power from  $V_{1MON}$ . The part will resume operational when the device junction temperature returns to normal.

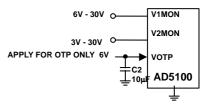

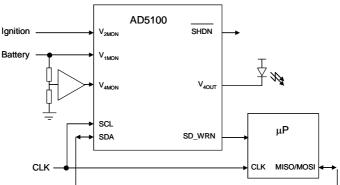

For automotive applications, proper external protections on the AD5100 are needed in order to ensure reliable operation. The  $V_{1MON}$  will likely be used for battery monitoring. The  $V_{2MON}$  will likely be used for ignition switch or other critical inputs. As a result, these inputs may need additional protections such as EMI, loaddump, and ESD protections. In addition, battery input also requires reverse battery protection and short circuit fuse protection, see Figure 19.

#### ESD Protection

It is common to require a contact rating of  $\pm 8kV$  and a noncontact or air rating of  $\pm 15kV$  ESD protection for the automotive electronics. As a result, a ESD rated protection device must be used such as MMBV27VCL, a dual 40W TVS (Transient Voltage Suppressor) at the V<sub>1MON</sub> and V<sub>2MON</sub>.

### Load Dump Protection

A load dump is a severe overvoltage surge that occurs when the car battery is being disconnected from a spinning alternator and the resulting long-duration, high-voltage surge introduced into the supply line. As a result, external load dump protection is recommended. Typically the load dump overvoltage lasts for few hundreds millisecond and peaks at around 40V to 70V while current can be as high as 1A. As a result, a load dump rated TVS D1 and D2 such as SMCJ17 are used to handle the surge energy. A series R is an in-line current limiting resistor, it should be adequate to limit the current without significant drop and yet small enough to not affect the input monitoring

### accuracy drop

### **Reverse Battery Protection**